|

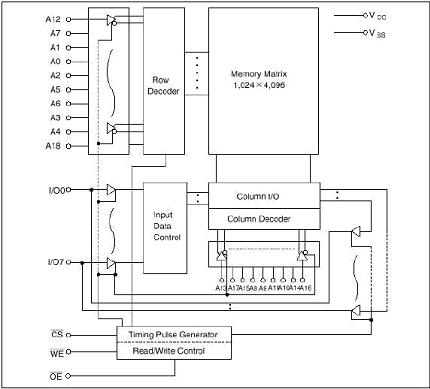

Aufbau eines Speicherchips

Als Beispiel eines Speicherchips soll hier ein 512K x 8 S-RAM betrachtet werden. Es existieren zwei Arten zum Bezeichnen der Kapazität eines Chip. Eine Möglichkeit ist mit der Angabe der verfügbaren Speicherzellen, z.B. 4M, womit aber nicht 4 Mbyte gemeint sind, sondern 4 Mbit. Besser ist die Angabe 512 Kx8, mit der die Busbreite gekennzeichnet wird. Üblich ist x1, x4, x8 und x16, meinstens aber wird x8 benutzt. Um eine Busbreite von 16 bit abzudecken werden zwei 8 Bit Speicherbausteine benötigt.

Dieser Speicherbaustein besitzt eine Kapazität von über 4 Millionen Speicherplätzen. Es sind demzufolge 4 Millionen Flip-Flop integriert. Durch die x8 Organisation werden pro Zugriff jeweils 8 Bit gemeinsam geschrieben oder gelesen. Ein Speicherchip besteht immer aus Adress-, Daten- und Steuerleitungen. Adressleitungen A0-A18: Jede Speicherstelle ist an einer bestimmten Adresse. Zum Bestimmen, auf welche Adresse zugegriffen werden soll, wird das entsprechende Bitmuster angelegt. Bei einem Chip mit 19 Adressleitungen sind 219 Adressen möglich, also 524'288 Adressen mit je 8 Bit oder 512 Kbyte (Achtung, K=1024!). Meist werden die Adressen hexadezimal dargestellt, also die tiefste Adresse 00000h und die höchste 7EEEEh. Datenleitung (I/O - Leitungen) Wie der Name sagt, werden die Datenleitungen die Daten ausgetauscht. Bei einer x8-Organisation sind es 8 Datenleitungen, beim ROM unidirektional (nur Lesen) und beim RAM bidirektional. Steuersignale (/CS /WE /OE) Mit den Steuersignale wird dem Chip mitgeteilt, welche Operation durchgeführt werden soll. __ CS Chip Select, der Speicherchip reagiert nur, wenn dieses Signal low ist. Dieses Signal wird meist mit einer externen Logik erzeugt, um mehrer Speicherchips zu kaskadieren.

___ WE Write Enable, wenn dieses Signal low ist, wird das Datum, das an D0-D7 liegt an die Adresse, die mit A0-A18 bestimmt wird, geschrieben.

___ OE Output Enable, wenn dieses Signal low ist, wird der Inhalt der Speicherzelle, die mit den Adressleitungen A0-A18 selektiert ist, an D0-D7 ausgegeben.

|

|

|